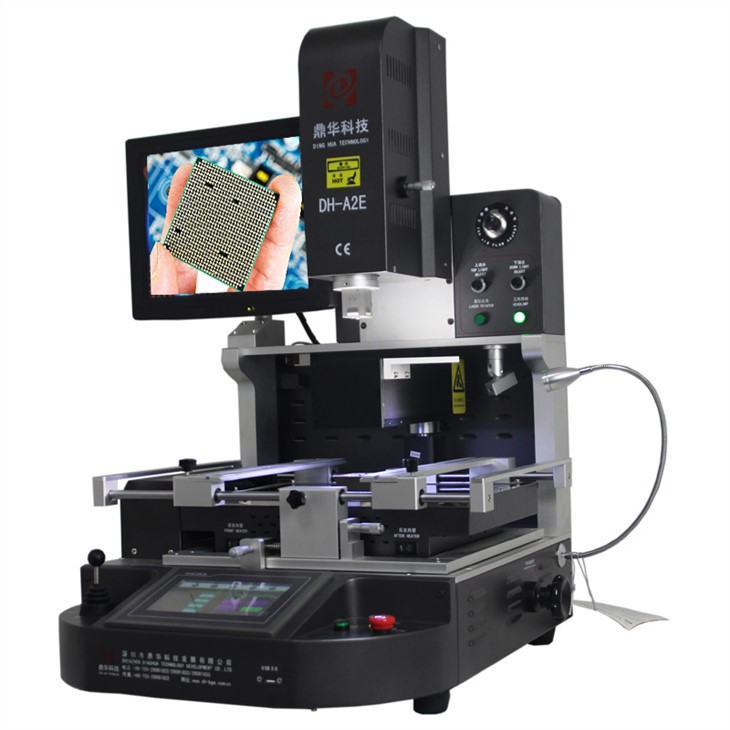

สถานีปรับปรุง BGA ออปติคัลอัตโนมัติ

ใช้กันอย่างแพร่หลายในการซ่อมระดับชิปสำหรับเมนบอร์ดของมือถือ แล็ปท็อป คอมพิวเตอร์ ทีวี เครื่องปรับอากาศ ฯลฯ มีอัตราการซ่อมแซมที่ประสบความสำเร็จสูงและระบบอัตโนมัติในระดับสูงและประหยัดความพยายามของมนุษย์ เราเป็นผู้ผลิตมืออาชีพของเครื่องนี้และมีเครื่องนี้อยู่ในสต็อก

คำอธิบาย

สถานีปรับปรุง BGA ออปติคัลอัตโนมัติ

1.Application ของ Auto Optical BGA Rework Station

เมนบอร์ดของคอมพิวเตอร์ สมาร์ทโฟน แล็ปท็อป MacBook ลอจิกบอร์ด กล้องดิจิตอล เครื่องปรับอากาศ ทีวี และอุปกรณ์อิเล็กทรอนิกส์อื่นๆ

อุปกรณ์จากอุตสาหกรรมการแพทย์ อุตสาหกรรมสื่อสาร อุตสาหกรรมรถยนต์ ฯลฯ

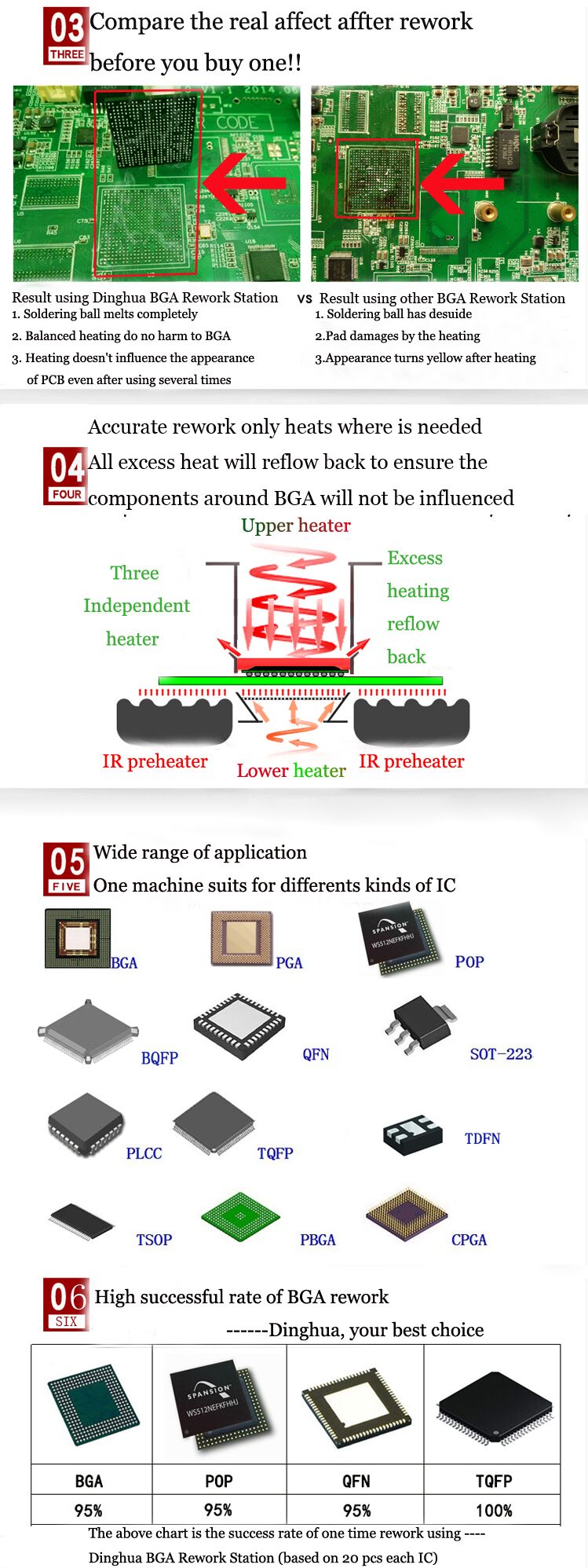

เหมาะสำหรับชิปประเภทต่างๆ: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, ชิป LED

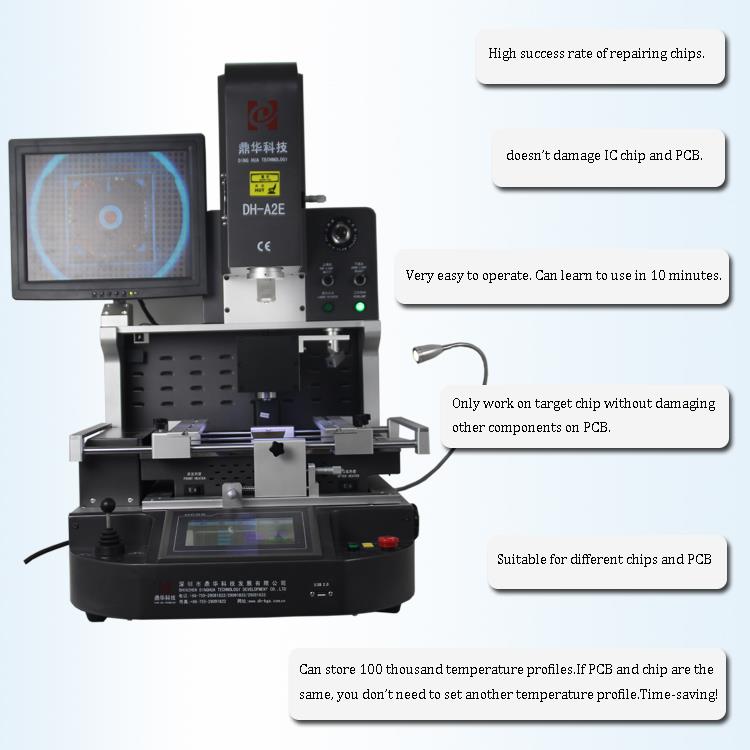

2. คุณสมบัติผลิตภัณฑ์ของสถานีปรับปรุง BGA ออปติคอลอัตโนมัติ

• อัตราความสำเร็จสูงในการซ่อมระดับชิป กระบวนการถอดบัดกรี ติดตั้ง และบัดกรีเป็นไปโดยอัตโนมัติ

• สามารถรับประกันการจัดตำแหน่งที่แม่นยำของทุกจุดบัดกรีด้วยกล้อง CCD การจัดตำแหน่งแบบออปติคัล

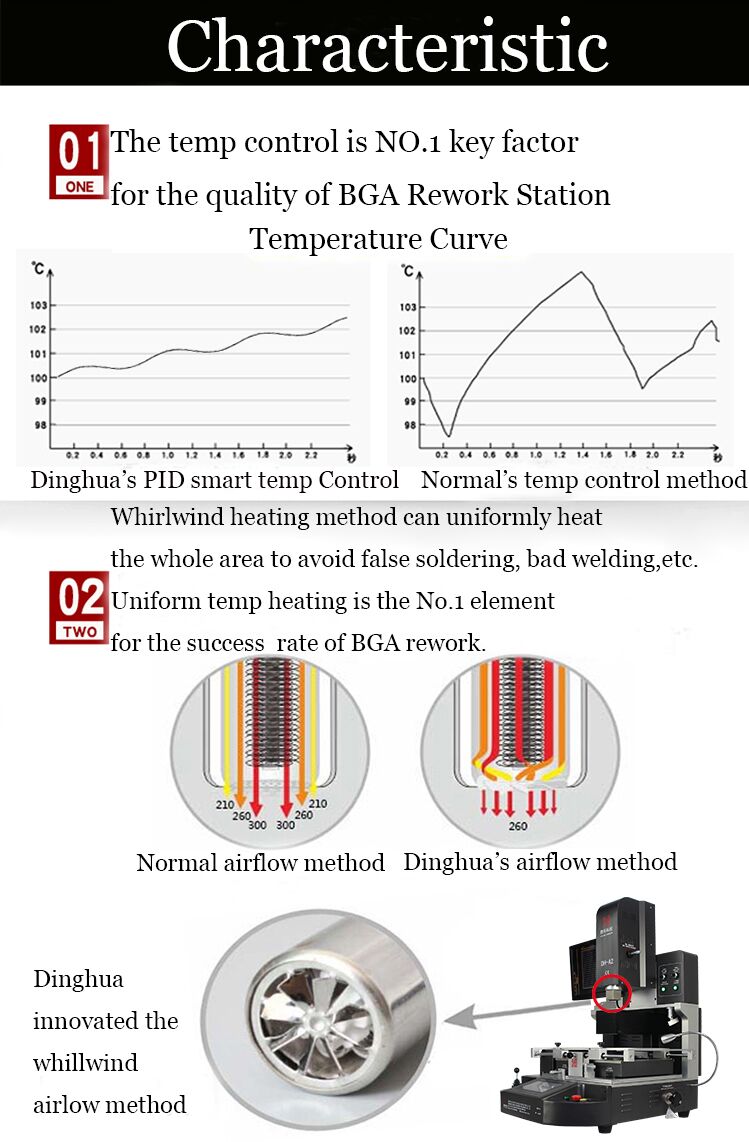

• มั่นใจได้ถึงการควบคุมอุณหภูมิที่แม่นยำด้วยพื้นที่ทำความร้อนอิสระ 3 แห่ง เครื่องสามารถตั้งค่าและบันทึก

โปรไฟล์อุณหภูมิ 1 ล้าน

• สูญญากาศในตัวในหัวจับยึดจะเก็บชิป BGA โดยอัตโนมัติหลังจากเสร็จสิ้นการบัดกรี

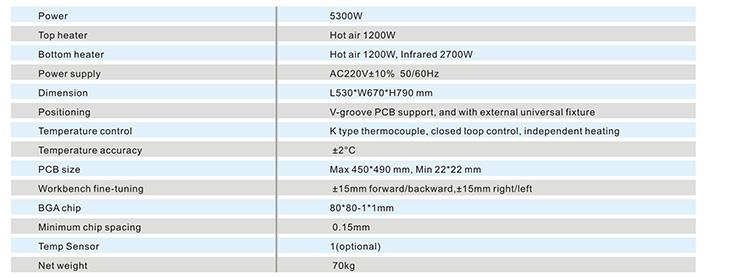

3. ข้อกำหนดของสถานีปรับปรุง BGA ออปติคอลอัตโนมัติ

4.รายละเอียดของสถานีปรับปรุง BGA ออปติคัลอัตโนมัติ

กล้อง CCD (ระบบจัดตำแหน่งแสงที่แม่นยำ); 2.จอแสดงผลดิจิตอล HD; 3. ไมโครมิเตอร์ (ปรับมุมชิป) ;

4.3 เครื่องทำความร้อนอิสระ (ลมร้อน & อินฟราเรด) ; 5. การวางตำแหน่งด้วยเลเซอร์ ; 6. อินเทอร์เฟซหน้าจอสัมผัส HD, การควบคุม PLC;

7. ไฟหน้าแบบ LED ; 8.จอยสติ๊กควบคุม

5.ทำไมต้องเลือกสถานีปรับปรุง BGA ออปติคัลอัตโนมัติของเรา

6.ใบรับรองสถานีปรับปรุง BGA ออปติคัลอัตโนมัติ

7. การบรรจุและจัดส่งสถานีปรับปรุง BGA ออปติคอลอัตโนมัติ

8. คำถามที่พบบ่อย

วิธีทดสอบชิป?

การทดสอบชิประดับระบบเบื้องต้น

SoC นั้นขึ้นอยู่กับกระบวนการระดับไมโครรอนที่ลึก ดังนั้นการทดสอบอุปกรณ์ Soc ใหม่จึงต้องใช้แนวทางใหม่ทั้งหมด เพราะแต่ละส่วนประกอบการทำงาน

มีข้อกำหนดในการทดสอบของตัวเอง วิศวกรออกแบบต้องทำแผนการทดสอบตั้งแต่เนิ่นๆ ในกระบวนการออกแบบ

ต้องนำแผนการทดสอบแบบบล็อกต่อบล็อกสำหรับอุปกรณ์ SoC: เครื่องมือ ATPG ที่กำหนดค่าอย่างเหมาะสมสำหรับการทดสอบลอจิก เวลาทดสอบสั้น ใหม่ความเร็วสูง

โมเดลข้อผิดพลาดและการทดสอบหน่วยความจำหลายตัวหรืออาร์เรย์ขนาดเล็ก สำหรับสายการผลิต วิธีการวินิจฉัยไม่เพียงแต่พบข้อผิดพลาด แต่ยังแยกส่วน

โหนดที่ผิดพลาดจากโหนดการทำงาน นอกจากนี้ ควรใช้เทคนิคมัลติเพล็กซ์ทดสอบทุกครั้งที่ทำได้เพื่อประหยัดเวลาในการทดสอบ ในด้านการสูง

การทดสอบ IC แบบบูรณาการ เทคนิคการออกแบบที่สามารถทดสอบได้ของ ATPG และ IDDQ มีกลไกการแยกข้อผิดพลาดที่ทรงพลัง

พารามิเตอร์จริงอื่นๆ ที่จำเป็นต้องวางแผนล่วงหน้า ได้แก่ จำนวนพินที่ต้องสแกนและจำนวนหน่วยความจำที่ปลายพินแต่ละอัน

การสแกนขอบเขตสามารถฝังอยู่ใน SoC แต่ไม่จำกัดเฉพาะการทดสอบการเชื่อมต่อระหว่างกันบนบอร์ดหรือโมดูลหลายชิป

แม้ว่าขนาดชิปจะลดลง แต่ชิปก็ยังสามารถบรรจุทรานซิสเตอร์ได้หลายล้านถึง 100 ล้านตัว และจำนวนโหมดการทดสอบก็เพิ่มขึ้นเป็นประวัติการณ์

ระดับส่งผลให้รอบการทดสอบยาวขึ้น ปัญหานี้สามารถทดสอบได้ การบีบอัดโหมดเพื่อแก้ปัญหาอัตราส่วนการบีบอัดสามารถเข้าถึง 20 เปอร์เซ็นต์ถึง 60 เปอร์เซ็นต์ สำหรับงานขนาดใหญ่ในวันนี้

การออกแบบชิป เพื่อหลีกเลี่ยงปัญหาด้านความจุ จำเป็นต้องค้นหาซอฟต์แวร์ทดสอบที่สามารถทำงานบน 64-ระบบปฏิบัติการบิต

นอกจากนี้ ซอฟต์แวร์ทดสอบยังเผชิญกับปัญหาการทดสอบใหม่ที่เกิดจากกระบวนการย่อยระดับไมครอนที่ลึกและความถี่ที่เพิ่มขึ้น ในอดีตโหมดการทดสอบ ATPG สำหรับ

การทดสอบข้อผิดพลาดการปิดกั้นแบบคงที่ไม่สามารถใช้ได้อีกต่อไป การเพิ่มรูปแบบการทำงานให้กับเครื่องมือแบบเดิมทำให้ยากต่อการค้นหาข้อบกพร่องใหม่ๆ แนวทางที่ดีกว่าคือการ

จัดประเภทกลุ่มโหมดการทำงานที่ผ่านมาเพื่อพิจารณาว่าข้อบกพร่องใดไม่สามารถตรวจจับได้ จากนั้นสร้างโหมด ATPG เพื่อจับประเภทข้อบกพร่องที่ขาดหายไปเหล่านี้

เมื่อความสามารถในการออกแบบเพิ่มขึ้นและเวลาทดสอบต่อทรานซิสเตอร์ลดลง เพื่อค้นหาปัญหาเกี่ยวกับความเร็วและตรวจสอบเวลาของวงจร วิธีการทดสอบแบบซิงโครนัส

จะต้องได้รับการว่าจ้าง การทดสอบแบบซิงโครนัสต้องรวมโมเดลข้อบกพร่องหลายแบบ รวมถึงโมเดลชั่วคราว การหน่วงเส้นทาง และ IDDQ

บริษัทบางแห่งในอุตสาหกรรมเชื่อว่าการรวมข้อผิดพลาดการบล็อก การทำงาน และข้อผิดพลาดชั่วคราว/เส้นทางอาจเป็นกลยุทธ์การทดสอบที่มีประสิทธิภาพมากที่สุด สำหรับลึก

ชิปซับไมครอนและการทำงานความถี่สูง การทดสอบการหน่วงเวลาชั่วคราวและเส้นทางมีความสำคัญยิ่งกว่า

เพื่อแก้ปัญหาความแม่นยำของ ATE เมื่อซิงโครไนซ์แกนทดสอบและลดต้นทุน จำเป็นต้องค้นหาวิธีการใหม่ที่ทำให้อินเทอร์เฟซของ

อุปกรณ์ทดสอบ (การทดสอบการหน่วงเวลาชั่วคราวและเส้นทางต้องใช้นาฬิกาที่แม่นยำที่อินเทอร์เฟซอุปกรณ์ทดสอบ) ช่วยให้มั่นใจได้ว่าสัญญาณมีความแม่นยำเพียงพอในระหว่างการทดสอบ

เนื่องจากมีความเป็นไปได้สูงที่จะเกิดข้อบกพร่องจากการผลิตในบล็อกหน่วยความจำ SoC หน่วยความจำ BIST จึงต้องมีฟังก์ชันการวินิจฉัย เมื่อพบปัญหาแล้ว

หน่วยที่อยู่ที่มีข้อบกพร่องสามารถแมปกับหน่วยความจำสำรองของหน่วยที่อยู่สำรอง และที่อยู่ข้อบกพร่องที่ตรวจพบจะถูกละทิ้ง หลีกเลี่ยงการทิ้ง

ชิปราคาแพงทั้งหมด

การทดสอบบล็อกหน่วยความจำฝังตัวขนาดเล็กช่วยลดความจำเป็นในการเกทหรือลอจิกการควบคุมเพิ่มเติม ตัวอย่างเช่น เทคนิคการทดสอบการแปลงเวกเตอร์สามารถแปลง

โหมดการทำงานเป็นชุดของโหมดการสแกน

ซึ่งแตกต่างจากวิธี BIST อินพุตการทำงานของบล็อกหน่วยความจำบายพาสไม่ต้องการตรรกะเพิ่มเติม เนื่องจากไม่ต้องการตรรกะการทดสอบเพิ่มเติม SoC

วิศวกรฝ่ายพัฒนาสามารถใช้รูปแบบการทดสอบที่เคยเกิดขึ้นในอดีตซ้ำได้

เครื่องมือ ATPG ขั้นสูงไม่เพียงแต่ทดสอบมาโครแบบขนานเท่านั้น แต่ยังกำหนดว่ามีข้อขัดแย้งหรือไม่ ตลอดจนระบุรายละเอียดว่ามาโครใดที่สามารถทดสอบแบบขนานได้ และตัวใด

ไม่สามารถทดสอบมาโครแบบขนานได้ นอกจากนี้ยังสามารถทดสอบมาโครเหล่านี้ได้อย่างมีประสิทธิภาพแม้ว่านาฬิกามาโครจะเหมือนกับนาฬิกาสแกน (เช่น หน่วยความจำซิงโครนัส)

ในปัจจุบันมีจุดทดสอบไม่เพียงพอบนกระดานสองด้านที่มีความหนาแน่นสูง และชิปที่ซับซ้อนแต่ละตัวจะต้องติดตั้งวงจรสแกนขอบเขต ปราศจาก

การสแกนขอบเขต การค้นหาข้อบกพร่องในการผลิตในระดับบอร์ดนั้นค่อนข้างยากและไม่พบด้วยซ้ำ ด้วยการสแกนขอบเขต การทดสอบระดับบอร์ดจึงเป็นเรื่องง่ายมาก

และเป็นอิสระจากวงจรลอจิกภายในชิป การสแกนขอบเขตยังสามารถกำหนดค่าโหมด ATPG ให้กับห่วงโซ่การสแกนของชิปในทุกขั้นตอนของการผลิต